TM 11-7021-202-12

c. Floating Point Unit (FPU). The FPU section consists of three PCBs installed in the

processor card cage. The FPU performs floating-point arithmetic on data supplied by the

CPU and/or data in the internal floating-point accumulators. Data transfers to and from the

FPU are controlled by the CPU, which also instructs the FPU as to the type of operation to

be performed. The actual execution of the floating-point instruction is independent of the

CPU. The FPU is monitored by the CPU to determine when the operation has been

completed and the result is available. The FPU does not have direct access to memory.

d.

Central Processing Unit (CPU). The CPU section consists of four PCBs. It

decodes and initiates execution of all instructions and performs all fixed-point arithmetic and

memory-reference operations. Its principal functional components include the Arithmetic

Logic Unit (ALU) and its input and output bus, the Prefetch Processor (PFP) and its bus, the

asynchronous communications interface for the system terminal, and the memory bus

e.

Input/Output Section. The input/output (I/O) section is made up of processor

slots--A1 through A8. Interface modules are installed in these slots to allow the processor to

interface with equipment external to the processor.

f.

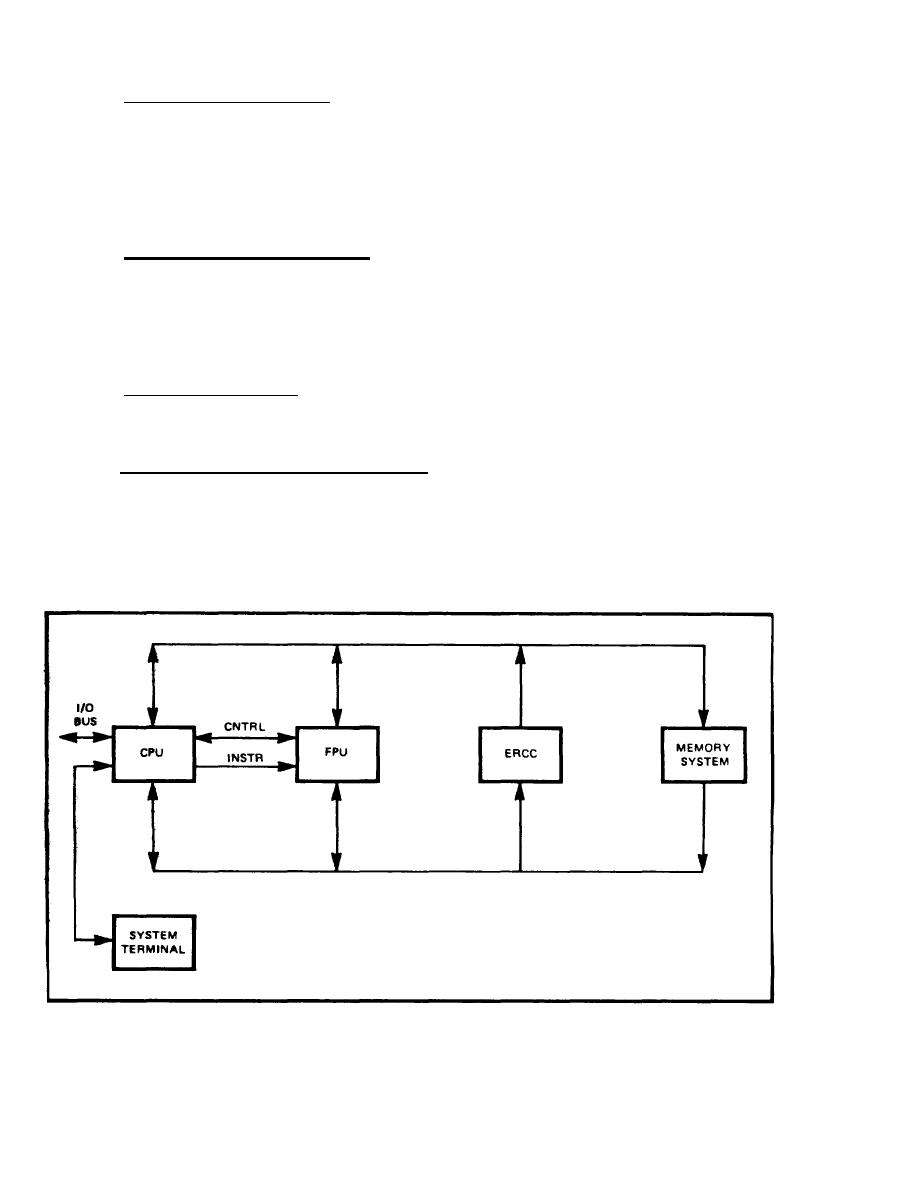

Major Subsystems and System Buses. The diagram to follow shows a simplified

representation of the functional sections (subsystems) within the processor and the principal

buses over which data is exchanged between the sections. There are two principal internal

buses: Memory In (MEMIN) and Memory Out (MEMOUT), and one principal external bus, the

I/O Bus.

EL9JY006

1-18